Active-HDL — это среда, предназначенная для разработки, моделирования и тестирования проектов для программируемых логических интегральных схем.

Введение

В течение последних десятилетий происходит необычайно быстрое развитие информационных технологий, базой которых являются вычислительное оборудование, системы и сети. Проектирование аппаратного обеспечения вычислительной техники сегодня основывается на информационных технологиях, которые позволяют описать цифровые модули на языках высокого уровня, осуществлять логическое и схемотехническое моделирование при учёте различных характеристик, температурных условий и многого другого.

Отдельные модули электронных вычислительных машин (ЭВМ) первых поколений были выполнены на основе цифровых микросхемах средней степени интеграции, которые размещались на двухслойных или многослойных печатных платах. Разработка функционального модуля выполнялась вручную, далее нужно было изготовить макет или опытный образец, который затем подвергался испытаниям, после чего следовала его настройка в экспериментах на стенде.

На кристаллах сегодняшних больших интегральных схем (БИС) может разместиться множество функциональных модулей старых ЭВМ, включая и цепи межблочных соединений. Проектирование и тестирование подобных кристаллов может быть реализовано только при помощи методов математического моделирования с применением передового компьютерного оборудования.

Современные международные стандарты, определяющие правила описания цифровой аппаратуры, то есть Hardware Description Language (HDL), предполагают использование языков высокого уровня, таких как, VHDL и VERILOG. С помощью эти языков может быть описано любое цифровое устройство, а далее проведено логическое моделирование работы данного устройства на компьютере. После того как будет достигнуто правильное функционирование модели, можно переходить к следующему этапу проектных работ, а именно, формированию структурной организации интегральных схем или конфигурации программируемых логических интегральных схем (ПЛИС).

Существует ряд известных систем автоматизированного проектирования (САПР), в том числе, пакет Active-HDL, который позволяет формировать описание цифровых устройств на языках VHDL и VERILOG, а далее осуществлять их логическое моделирование на компьютерном оборудовании.

Моделирование цифровых узлов в программе Active-HDL

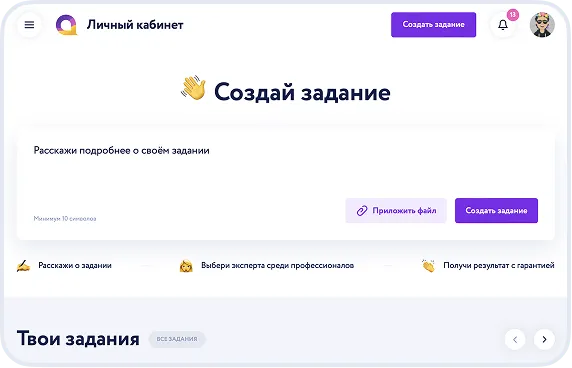

Программная среда логического моделирования цифровых устройств Active-HDL считается мощнейшим передовым средством, способным помочь в проектировании и моделировании, которое ориентировано на языки высокого уровня VHDL и VERILOG. Мастер проекта (Design Wizard) служит для того, чтобы создать проект цифрового модуля. Окно «Начало» должно автоматически появиться после запуска программы. Для того чтобы создать новый проект, в этом окне следует установить курсор мышки на пункт меню «Создать новый проект» и нажать клавишу ОК. Для того чтобы продолжить работу с ранее созданным проектом (клавиша «More design»), следует выбрать заголовок проекта в рабочем каталоге.

При формировании нового проекта должно появиться окно «Мастер нового проекта», в котором следует курсором указать на позицию «Создать пустой проект» и нажать кнопку «Далее» (Next), как показано на рисунке ниже.

Рисунок 1. Окно программы. Автор24 — интернет-биржа студенческих работ

Рисунок 2. Окно программы. Автор24 — интернет-биржа студенческих работ

Далее необходимо указать способ ввода проекта (установить в окне HDL), а также задать в окне заголовка имея проекта и имя рабочей папки проекта. «Мастер нового проекта» предоставляет возможность создания новых файлов проекта, которые содержат шаблон для формирования VHDL-описания проекта на базе информации, заносимой в диалоговом режиме при дальнейшей работе с мастером. Помимо этого, присутствует возможность добавления командой Add в проект ранее сформированных файлов, включая файлы из иных проектов. Затем по нажатию клавиши «Далее» (Next) необходимо перейти к следующему окну Мастера, в котором следует задать заголовок нового проекта. В итоге будет доступен «Мастер процесса проектирования», как показано на рисунке ниже.

Рисунок 3. Окно программы. Автор24 — интернет-биржа студенческих работ

Чтобы продолжить работу над проектом следует нажать на HDE, сделать выбор в возникшем окне язык VHDL и нажать ОК, что означает переход к окну «Мастер новых исходных файлов». Данный мастер предоставляет возможность создания шаблона VHDL-описания цифрового устройства, где могут быть указаны его порты и подключенные библиотеки.

Сформируем как пример VHDL-описание D-триггера с синхронизацией по переднему фронту синхроимпульса:

Рисунок 4. VHDL-описание D-триггера. Автор24 — интернет-биржа студенческих работ

Сигнал на выходе Q D-триггера должен соответствовать сигналу на входе D в момент появления переднего фронта синхроимпульса С и появится на выходе Q с задержкой, к примеру, в пять наносекунд (нс). Сигнал на инвертированном выходе Q ⃑ тоже обязан выдерживать задержку в пять нс.

Затем следует нажать кнопку «Далее» (Next) в окне «Мастер новых исходных файлов», как показано на рисунке ниже.

Рисунок 5. Окно программы. Автор24 — интернет-биржа студенческих работ

А затем нужно перейти к следующему окну Мастера, в окнах которого следует ввести имя файла VHDL-описания (к примеру, REDFF_1. vhd), имя устройств (к примеру, REDFF_1) и имя архитектуры устройства (к примеру, REDFF_behavior_1).

Редактор HDL позволяет упростить процедуру формирования описания за счёт следующих аспектов:

- Автоматического завершения ключевых слов (к примеру, Entity).

- Автоматического переноса шаблона оператора в окно Редактора HDL из Помощника по языку (Language Assistant), для чего следует после ввода имени шаблона нажать Ctrl+Enter.

Правильность VHDL-описания может быть проверена при его компиляции (compile). Для выполнения компиляции следует выбрать ниспадающее меню Design, а далее пункт Compile (или выбрать F11). В случае отсутствия ошибок нет, в нижнем окне консоли (Console) системы Active-HDL должно появиться сообщение о том, что компиляция осуществлена успешно.