Комбинационные логические схемы

Комбинационная логическая схема – это схема, которая преобразует входные двоичные сигналы в выходные логические сигналы в соответствии с логической функцией.

В стационарном состоянии выходные сигналы определены однозначно и никак не зависят от предыстории. Комбинационные логические схемы, в отличии от вентилей, могут иметь несколько выходов. Они могут быть реализованы уровнями: вентильным, блочным, транзисторным. К основным параметрам оптимизации комбинационной логической схемы относятся потребляемая мощность, быстродействие, площадь, которую занимает схема в кристалле. К достоинствам комбинационных логических схем относятся простота проектирования, отсутствие потребления в статике, помехозащищенность, полный размах выходного напряжения, связь выхода с питанием. Основными недостатками комбинационных логических схем являются: зависимость задержки входов и предыстории, удвоение входов, наличие сквозных токов переключения, различия в подвижностях. Типовыми комбинационными схемами являются:

- Драйвер - магистральный усилитель. Целесообразно исключать входные токи.

- Шифратор - преобразователь кода, который содержит только одну единицу в двоичное число, в частности, десятичные числа в двоичную систему счисления, при этом каждому входу может быть поставлено в соответствие десятичное число, а набор логических сигналов будет соответствовать определенному логическому коду. Шифратор может быть использован для перевода десятичных чисел, которые набираются на клавиатуре кнопочного пульта управления, в двоичные числа.

- Дешифратор - для каждой входной комбинации М разрядного числа он переводит единицу в одну выходную шину из m = 2^M.

- Мультиплексор - преобразует параллельный код в последовательный.

- Демультиплексор - преобразует последовательный код в параллельный.

- Сумматор.

Синтез комбинационных логических схем

Синтез – это проектирование и разработка заданного устройства согласно определенных правил, которые обеспечивают оптимальное решение поставленных задач.

Синтез комбинационной логической схемы состоит из следующих этапов:

- Анализ технического задания.

- Составление таблицы истинности.

- Запись логических функций.

- Минимизация логических функций.

- Разработка схемы.

- Описание устройства на языке описания аппаратных средств.

- Разработка тестовых сигналов. Построение временных диаграмм.

Исходные данные для синтеза комбинационной логической схемы могут быть заданы в виде словесного описания выполняемой функции или в виде таблицы истинности. Началом процесса синтеза комбинационной логической схемы является однозначное и четкое определение закона функционирования синтезируемой схемы. Определяются входные и выходные сигналы и изображается символ разрабатываемого устройства, пример которого показан на рисунке ниже.

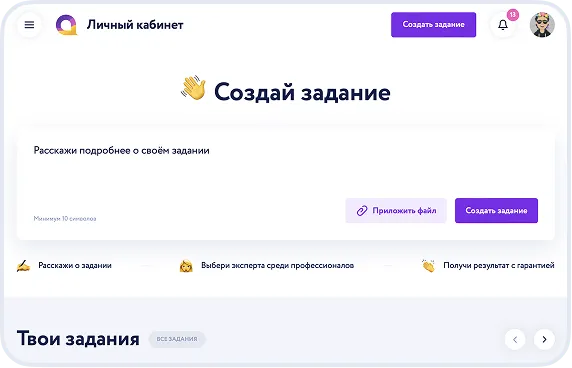

Рисунок 1. Символ разрабатываемого устройства. Автор24 — интернет-биржа студенческих работ

В соответствии с ГОСТом символы логических составляющих изображаются в сетке 2,5 миллиметра, входы слева, выходы справа, а в среднем поле изображаются символические отображение функционального назначения устройства. В общем случае таблица истинности составляется разработчиком на основе анализа технического задания. Комбинационная логическая схема может быть описана логическими функциями, которые представлены в совершенной дизъюнктивной нормальной форме и совершенной конъюнктивной нормальной форме. Название функции определяет ряд правил для ее записи. Логическая функция в совершенной дизъюнктивной нормальной форме представляет собой дизъюнкцию вспомогательных функций - минтермов.

Минтерм – это произведение всех входных сигналов, которые записаны без инверсии или с инверсией, равное единице только на заданном наборе аргументов.

Форма записи логической функции в виде совершенной конъюнктивной нормальной форме представляет собой произведение вспомогательных функций или макстермов. Макстермы является дизъюнкцией всех входных сигналов, которые записаны без инверсии или с инверсией, равной нулю только на заданном наборе аргументов. Минимизация логических функций позволяет снизить аппаратные затраты при построении комбинационной схемы, в данном случае увеличиваются надежность и быстродействие проектируемого устройства. Минимизация может быть осуществлена аналитически, с использованием теорем и законов алгебры логики. Метод Карно позволяет осуществлять операции склеивания и найти минимальные конъюнктивные и дизъюнктивные формы. Логические функции в минимальной конъюнктивной форме или минимальной дизъюнктивной форме используется для дальнейшего построения схемы проектируемого устройства. Затем строятся временные диаграммы с использованием таблицы истины и минимизированных логических функций.